RECENT BLOG Post

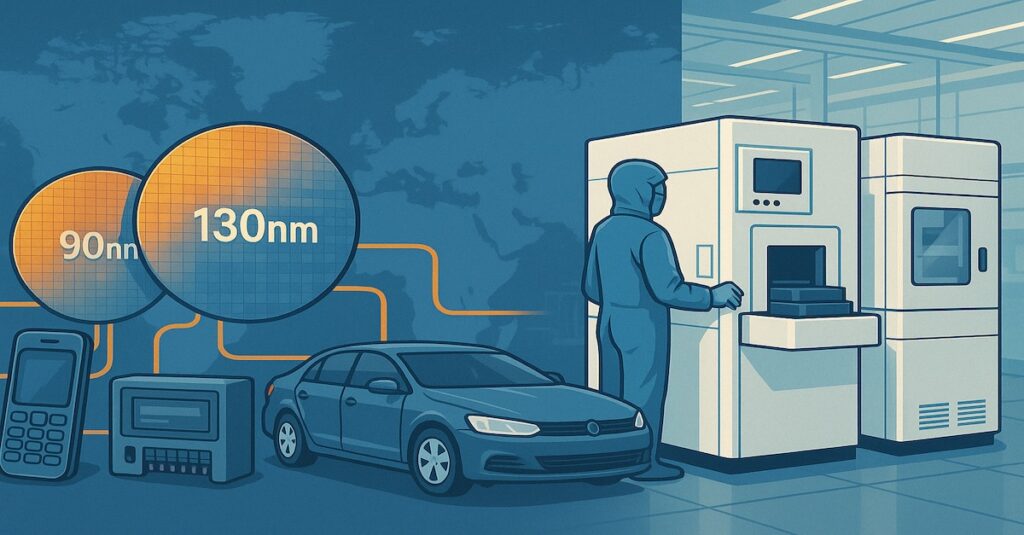

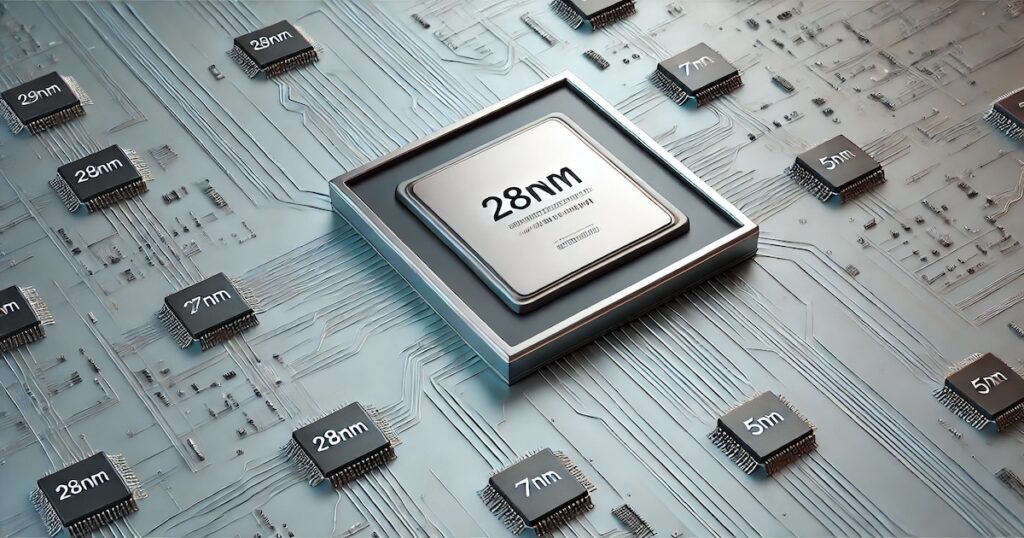

4o How Large Is The Mature Node Economy The focus immediately shifts to cutting-edge nodes such as 3nm or

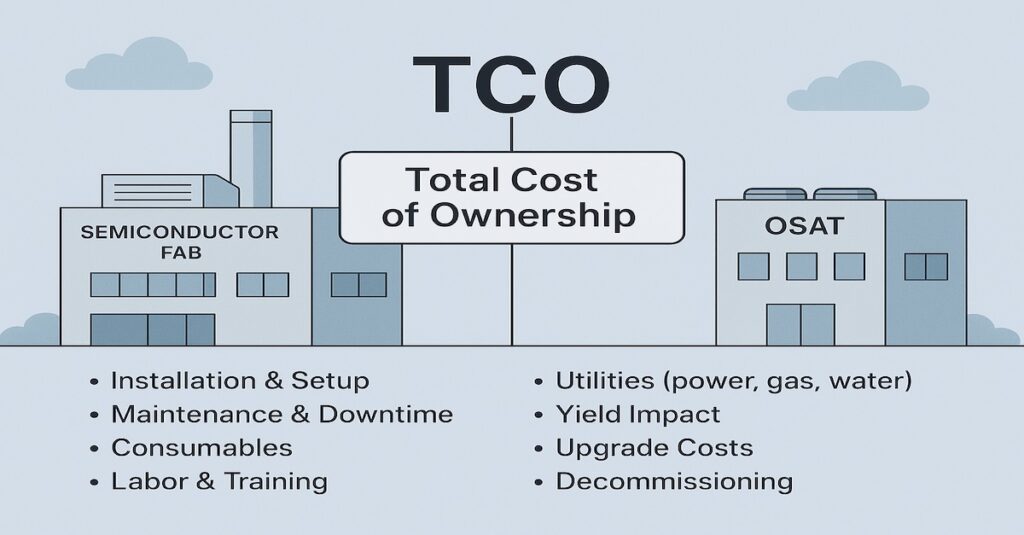

4o What Is Total Cost of Ownership (TCO)? In the semiconductor industry, the cost of a tool, IP block,

4o What Is A Semiconductor Smart Factory? If you have spent time reading developments in the semiconductor industry, you

DALL-E The Rise Of Open-Source Semiconductor Design Traditionally, semiconductor design has been a highly proprietary field dominated by closed

DALL-E The AI Debate Artificial Intelligence (AI) often sparks divided opinions as a groundbreaking innovation or technological hype. At

DALL-E Fundamental Concepts of Semiconductor Thermography Semiconductor thermography is a non-destructive measurement technique that quantifies and visualizes temperature variations

DALL-E Simulation In Semiconductor Development The semiconductor industry constantly evolves, increasing design complexity and high manufacturing costs. Traditional methods

DALL-E Semiconductor Reliability Matters The semiconductor industry thrives on precision, performance, and longevity, from microcontrollers to processors, semiconductors power

DALL-E Importance Of Semiconductor Node Selection Choosing the right technology node is among the most critical engineering and business