Data-Driven Approaches To Yield Prediction In Semiconductor Manufacturing

Published By: Electronics Product Design And TestDate: March 2025Media Type: Online Media Website And Digital Magazine

#chetanpatil – Chetan Arvind Patil

Published By: Electronics Product Design And TestDate: March 2025Media Type: Online Media Website And Digital Magazine

Published By: Electronics Product Design And TestDate: February 2025Media Type: Online Media Website And Digital Magazine

Published By: Electronics Product Design And TestDate: January 2025Media Type: Online Media Website And Digital Magazine

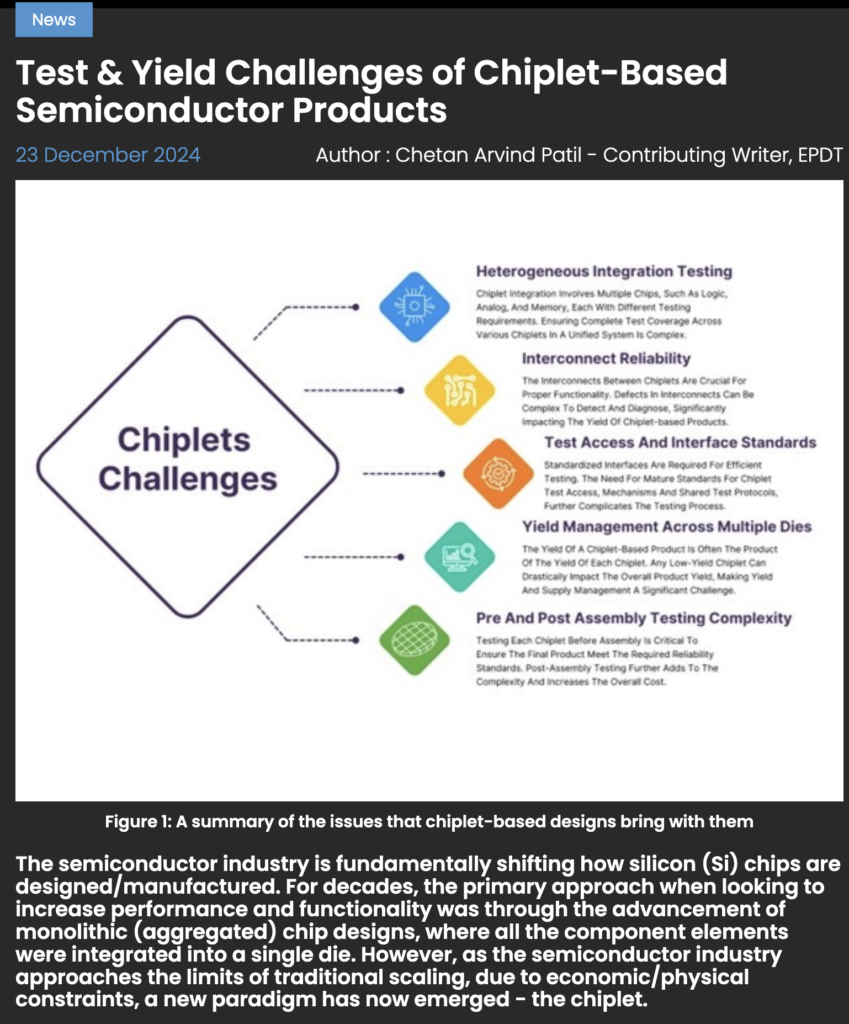

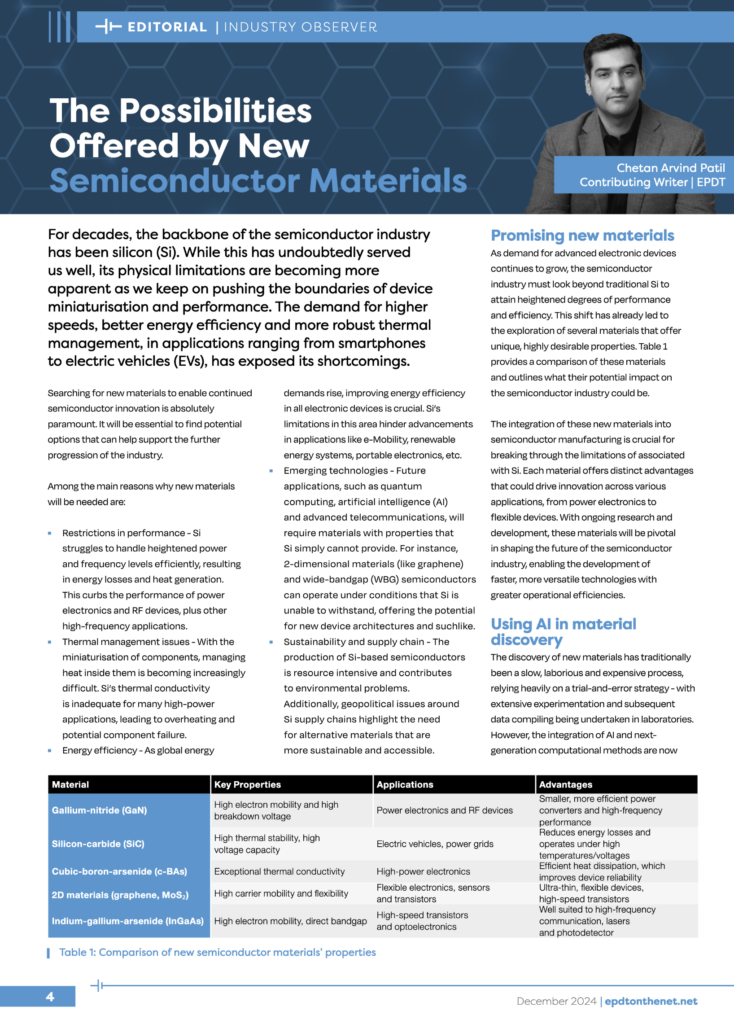

Published By: Electronics Product Design And TestDate: December 2024Media Type: Online Media Website And Digital Magazine

Published By: Electronics Product Design And TestDate: December 2024Media Type: Online Media Website And Digital Magazine

Published By: Electronics Product Design And TestDate: November 2024Media Type: Online Media Website And Digital Magazine

Published By: ScienceIndiaDate: October 2024Media Type: Online Media Website And Digital Magazine

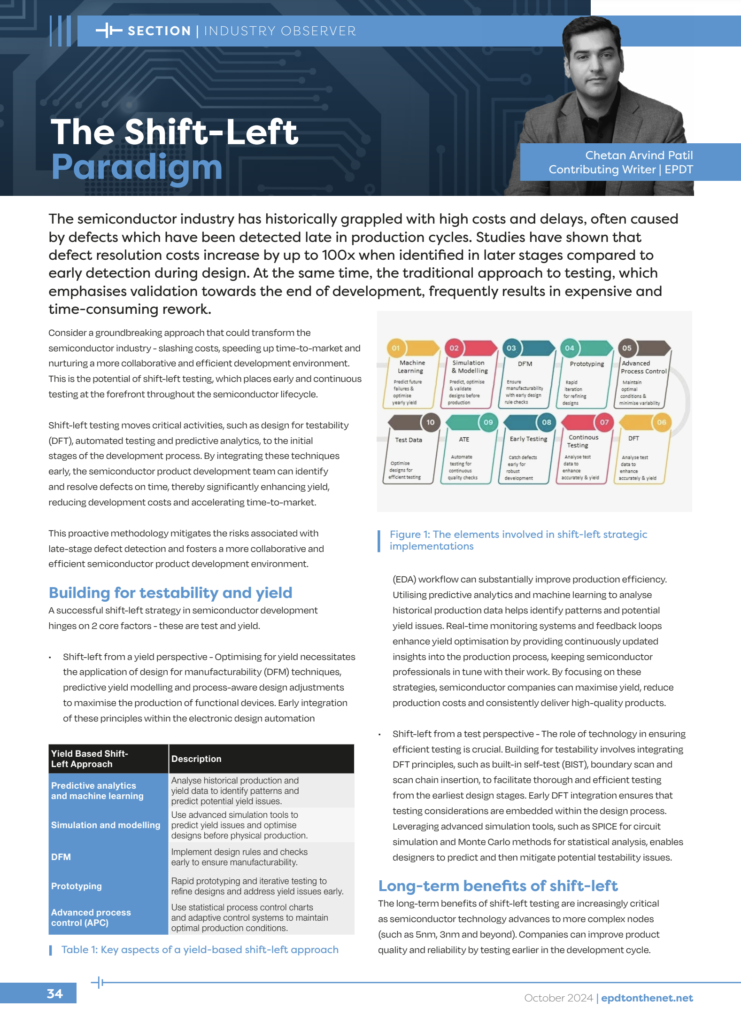

Published By: Electronics Product Design And TestDate: October 2024Media Type: Online Media Website And Digital Magazine

Published By: Silicon IndiaDate: 9th September 2024Media Type: Digital

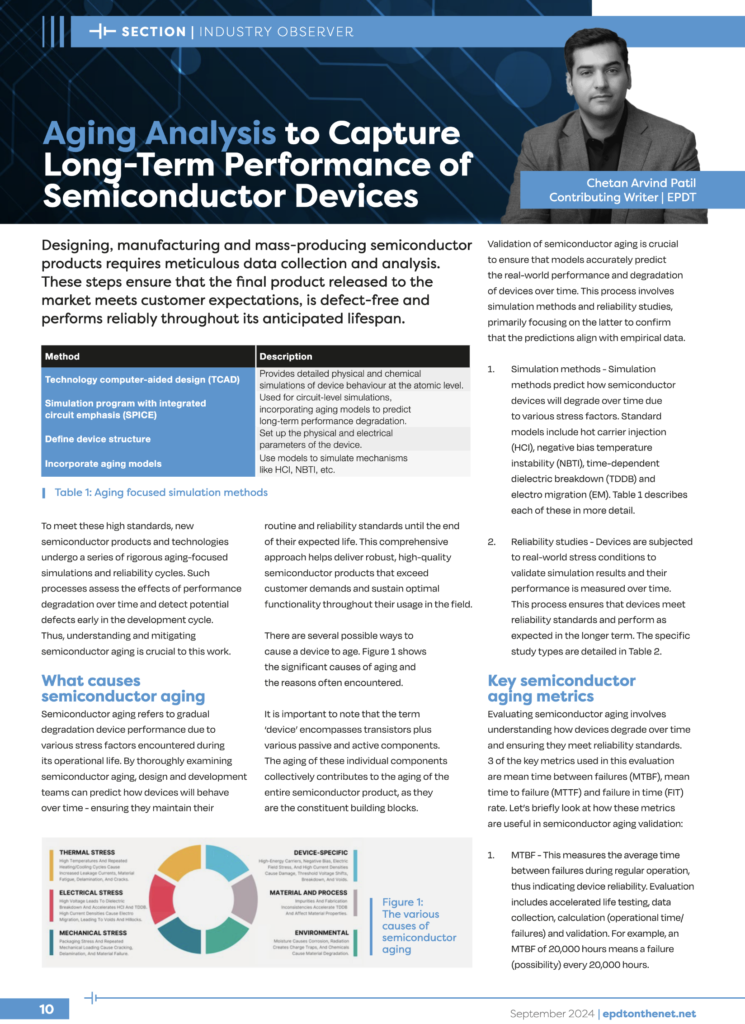

Published By: Electronics Product Design And TestDate: September 2024Media Type: Online Media Website And Digital Magazine

Hi, I am Chetan Arvind Patil (chay-tun – how to pronounce), a semiconductor professional whose job is turning data into products for the semiconductor industry that powers billions of devices around the world. And while I like what I do, I also enjoy biking, working on few ideas, apart from writing, and talking about interesting developments in hardware, software, semiconductor and technology.

This work is licensed under a Creative Commons Attribution-NonCommercial-ShareAlike 4.0 International License. In other words, share generously but provide attribution.

Opinions expressed here are my own and may not reflect those of others. Unless I am quoting someone, they are just my own views.

DALL-E The Rise Of Open-Source Semiconductor Design Traditionally, semiconductor design has been a highly proprietary field dominated by closed

DALL-E The AI Debate Artificial Intelligence (AI) often sparks divided opinions as a groundbreaking innovation or technological hype. At

DALL-E Fundamental Concepts of Semiconductor Thermography Semiconductor thermography is a non-destructive measurement technique that quantifies and visualizes temperature variations

DALL-E Simulation In Semiconductor Development The semiconductor industry constantly evolves, increasing design complexity and high manufacturing costs. Traditional methods

DALL-E Semiconductor Reliability Matters The semiconductor industry thrives on precision, performance, and longevity, from microcontrollers to processors, semiconductors power