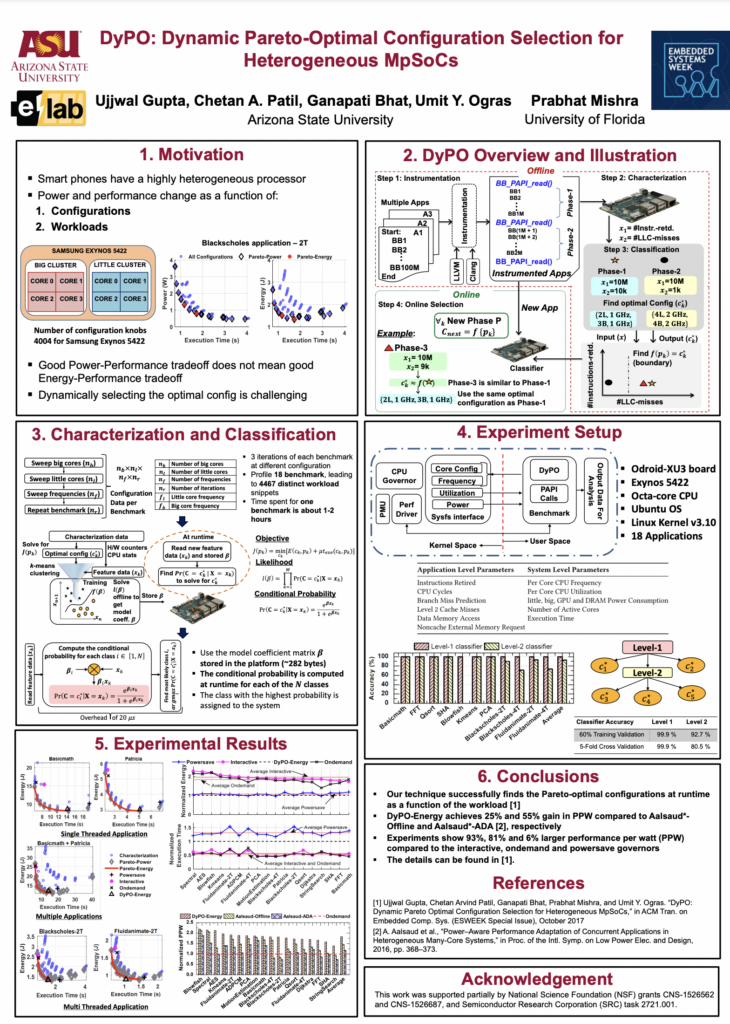

Modern multiprocessor systems-on-chip (MpSoCs) offer tremendous power and performance optimization opportunities by tuning thousands of potential voltage, frequency and core configurations. As the workload phases change at runtime, different configurations may become optimal with respect to power, performance or other metrics. Identifying the optimal configuration at runtime is infeasible due to the large number of workloads and configurations. This paper proposes a novel methodology that can find the Pareto-optimal configurations at runtime as a function of the workload. To achieve this, we perform an extensive offline characterization to find classifiers that map performance counters to optimal configurations. Then, we use these classifiers and performance counters at runtime to choose Pareto-optimal configurations. We evaluate the proposed methodology by maximizing the performance per watt for 18 single- and multi-threaded applications. Our experiments demonstrate an average increase of 93%, 81% and 6% in performance per watt compared to the interactive, ondemand and powersave governors, respectively.

DyPO: Dynamic Pareto-Optimal Configuration Selection for Heterogeneous MpSoCs

- | Published On:

Chetan Arvind Patil

Hi, I am Chetan Arvind Patil (chay-tun – how to pronounce), a semiconductor professional whose job is turning data into products for the semiconductor industry that powers billions of devices around the world. And while I like what I do, I also enjoy biking, working on few ideas, apart from writing, and talking about interesting developments in hardware, software, semiconductor and technology.

COPYRIGHT

2025

, CHETAN ARVIND PATIL

This work is licensed under a Creative Commons Attribution-NonCommercial-ShareAlike 4.0 International License. In other words, share generously but provide attribution.

DISCLAIMER

Opinions expressed here are my own and may not reflect those of others. Unless I am quoting someone, they are just my own views.

RECENT POSTS

4o How Large Is The Mature Node Economy The focus immediately shifts to cutting-edge nodes such as 3nm or

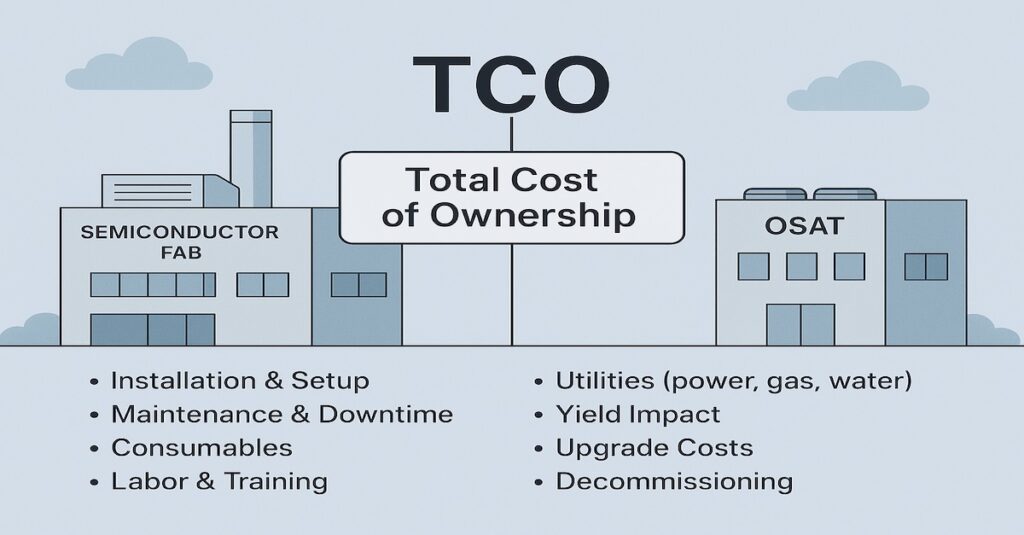

4o What Is Total Cost of Ownership (TCO)? In the semiconductor industry, the cost of a tool, IP block,

4o What Is A Semiconductor Smart Factory? If you have spent time reading developments in the semiconductor industry, you

DALL-E The Rise Of Open-Source Semiconductor Design Traditionally, semiconductor design has been a highly proprietary field dominated by closed

DALL-E The AI Debate Artificial Intelligence (AI) often sparks divided opinions as a groundbreaking innovation or technological hype. At