Networks-on-chip have become the standard interconnect solution to address the communication requirements of many-core chip multiprocessors. It is well-known that network performance and power consumption depend critically on the traffic load. The network traffic itself is a function of not only the application, but also the cache coherence protocol, and memory controller/directory locations. Communication between the distributed directory to memory can introduce hotspots, since the number of memory controllers is much smaller than the number of cores. Therefore, it is critical to account for directory memory communication, and model them accurately in architecture simulators. This paper analyzes the impact of directory memory traffic and different memory and cluster modes on the NoC traffic and system performance. We demonstrate that unrealistic models in a widely used multiprocessor simulator produce misleading power and performance predictions. Finally, we evaluate different memory and cluster modes supported by Intel Xeon-Phi processors, and validate our models on four different cache coherence protocols.Subodha Charles,

Exploration of Memory and Cluster Modes in Directory-Based Many-Core CMPs.

- | Published On:

Chetan Arvind Patil

Hi, I am Chetan Arvind Patil (chay-tun – how to pronounce), a semiconductor professional whose job is turning data into products for the semiconductor industry that powers billions of devices around the world. And while I like what I do, I also enjoy biking, working on few ideas, apart from writing, and talking about interesting developments in hardware, software, semiconductor and technology.

COPYRIGHT

2025

, CHETAN ARVIND PATIL

This work is licensed under a Creative Commons Attribution-NonCommercial-ShareAlike 4.0 International License. In other words, share generously but provide attribution.

DISCLAIMER

Opinions expressed here are my own and may not reflect those of others. Unless I am quoting someone, they are just my own views.

RECENT POSTS

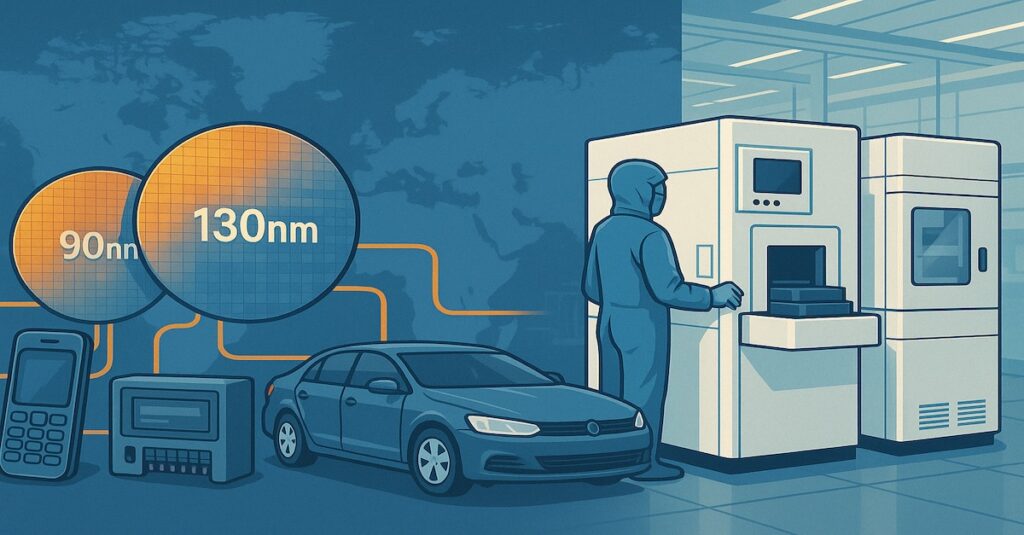

4o How Large Is The Mature Node Economy The focus immediately shifts to cutting-edge nodes such as 3nm or

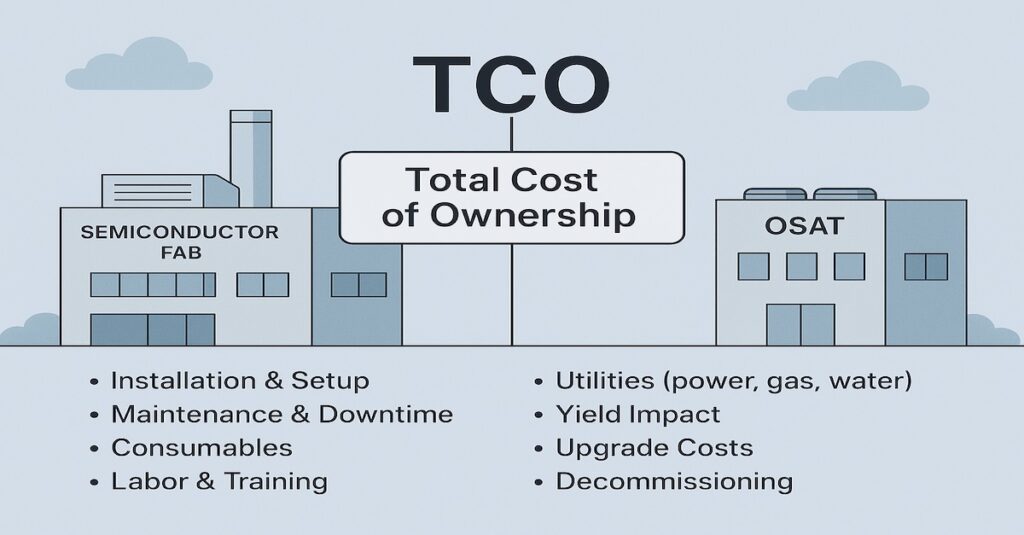

4o What Is Total Cost of Ownership (TCO)? In the semiconductor industry, the cost of a tool, IP block,

4o What Is A Semiconductor Smart Factory? If you have spent time reading developments in the semiconductor industry, you

DALL-E The Rise Of Open-Source Semiconductor Design Traditionally, semiconductor design has been a highly proprietary field dominated by closed

DALL-E The AI Debate Artificial Intelligence (AI) often sparks divided opinions as a groundbreaking innovation or technological hype. At