Photo by Florian Olivo on Unsplash

THE GROWTH OF HETEROGENEOUS INTEGRATION

The computer architecture design to cater the personal computing to data center needs has seen many changes over the last four decades. Computer architects have pushed the boundaries of designing novel ways to process data, which has lead to the manufacturing of advanced processing units (XPU) that are powering low to high-performance computing systems.

The growth of XPU is not only driven by the novel designs but also due to the shrinking transistor size. The advanced technology-node has allowed computer architects to take advantage of billions of transistors in the smaller area possible. With the ability to pack more transistors, the processing speed has increased, which has reduced the time taken to process user requests. All these hardware features combined with an elegant software system is powering the system to drive a rich user experience.

However, packing more transistors in the same area is hitting the wall. The benefits that Moore’s law provided a decade ago will not be applicable ten years down the line. Packing more transistors is not only leading to area-wall but is also adding power-wall, performance-wall, and thermal-wall. As more users come online, the expectation to provide real-time data processing will grow and this demands a new design and manufacturing approach for the next-gen XPU. The next-gen innovation should not only drive the required market growth and but must also ensure that the semiconductor industry never hits the usage-wall.

Heterogeneous Integration Is For Next-Gen XPU

On top of all this, the transistor size can not keep decreasing forever. The new technology-node also demands massive investment in the existing and new semiconductor fabrication facilities, thus pushing the semiconductor industry towards new XPU designs that uses a novel combination of technology-node and packaging solutions. These new types of CPUs are/will use heterogeneous integration for semiconductor designing and manufacturing.

There are two aspects of heterogeneous integration that any new emerging solution will have to consider before heterogeneous integration can be used to fabricate the next-gen XPU:

Design: Developing XPU with a heterogeneous integration approach needs different dies (sub-systems) to work in harmony. This demands cycle/time accurate communication between dies/blocks that may or may not come out of the same design team/company. To ensure all the dis-integrated systems can work in an integrated manner, requires a detailed design, verification, and testing approach. Without ensuring all the systems within the heterogeneous integration powered XPU working in synchronization, the end-product might not meet the expectation of the end-customers.

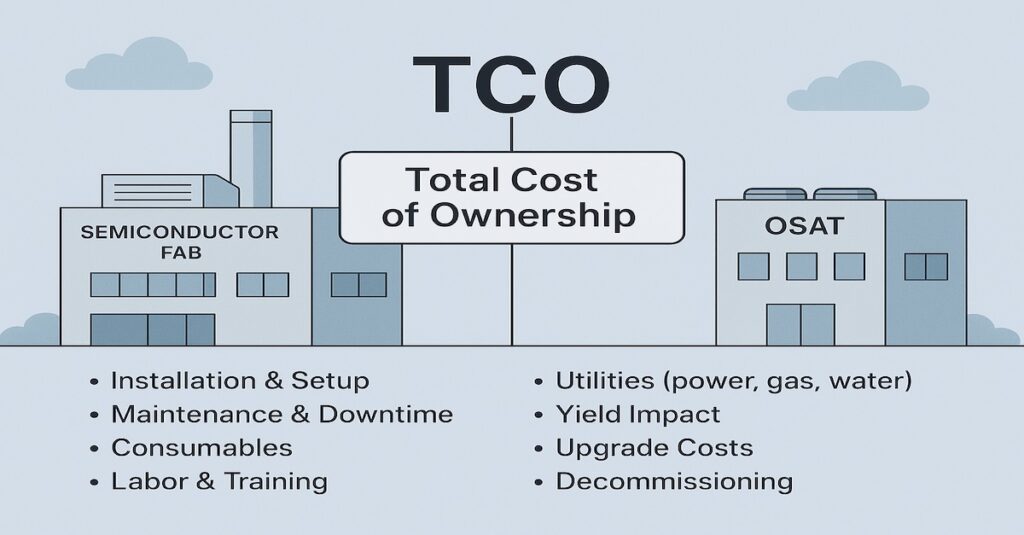

Manufacturing: Fabricating, packaging, and testing all the components of an XPU on a single die is a proven method. With heterogeneous integration, the dies (fabricated individually) will get integrated to form a single system. This will require a novel approach that is cost-effective and does not add a new bottleneck from a manufacturing point of view.

Heterogeneous integration and solutions around it are not new but will be when the industry moves towards large-scale adoption to design chips that follow the heterogeneous integration approach. The main reason is the bottlenecks and issues semiconductor companies without prior heterogeneous integration experience will face when they decide to venture into this territory.

Design and manufacturing are the two key areas that the emerging heterogeneous inspired XPU will have to focus on. However, there are several other challenges that both the existing and emerging solutions around heterogeneous integration will face.

THE CHALLENGES FOR HETEROGENEOUS INTEGRATION

Heterogeneous integration is touted as one of the More-Than-Moore solutions that can take away the need of shrinking transistor size further. However, there are few challenges to overcome when the XPUs are designed using a heterogeneous integration approach:

Data: The goal of any XPU is to ensure the data being processed flows across the blocks in the fastest possible time with near-zero latency. If the systems are going to be more heterogeneous and are stacked in such a way that they eventually have to communicate via a bus, then this may very well add data flow bottlenecks. This challenge can be overcomes via an optical interconnect system, but such solutions are not fully tested for a large-scale computing usage.

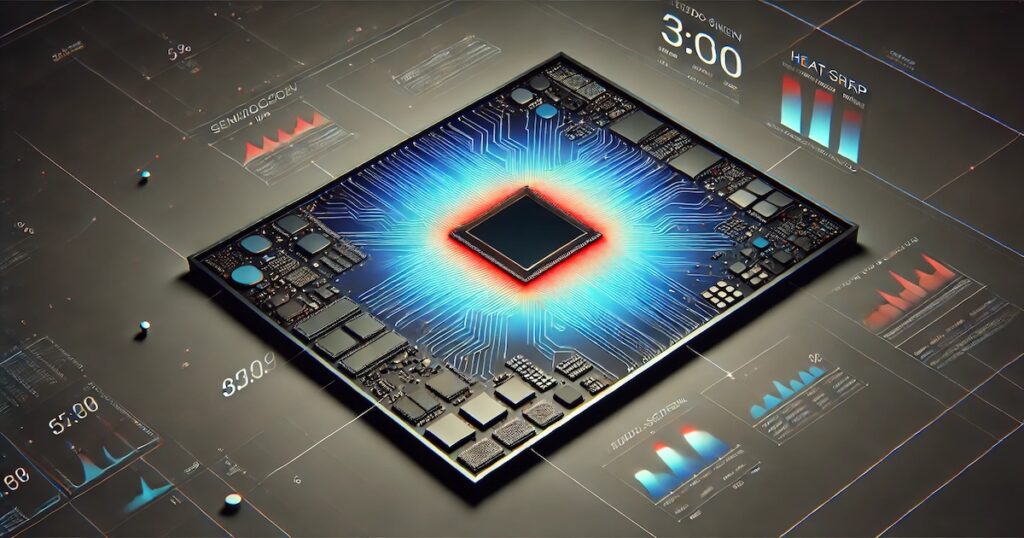

Power: Heterogeneous integration certainly provides avenues to overcome the challenges shrinking transistor size brings. However, the focus should also be on Performance-Per-Watt (PPW) to justify XPU designs that uses a heterogeneous integration approach. In the end, the goal of any processing unit like XPU is to provide maximum benefits at the lowest cost possible. Given, the demand to run more sophisticated graphics driven applications, the need to provide better PPW should be the priority of any heterogeneously integrated XPU.

Quality: XPU that will use heterogeneous integration will require qualification before production. In a monolithic chip, all the components are designed and fabricated together, which also gets qualified (JEDEC/AEC, etc.) for production use. However, with a heterogeneous approach, the singulated dies that form an integrated system will have to get qualified individually. This will increase the cost and time taken to execute the qualification plan, and might also raise the question on how different qualification criteria can be applied to integrated XPU.

Thermal: Controlling temperature ensures that there is no thermal runaway in any type of XPU. If heterogeneous integration will take the 3D approach, then managing die-to-die heat transfer can be a challenge. Fast heating will mean throttling the system often and will eventually impact the user experience.

Protocols: Heterogeneous integration also means integrating two different IPs. If the protocols to ensure smooth communication between these multiple dies are not defined and standardized across the industry, it might hinder the progress of next-gen XPU.

Packaging: Integrating all different die to eventually form a single system demands innovative packaging. While System-In-Package (SiP) based solutions are already out in the market, there is a need to test a different approach to packaging that ensures the area and thermal constraints are not leading to bottlenecks.

Above are few challenges that the next-gen XPU powered using heterogeneous integration may face. As more and more XPU design follow heterogeneous integration approach, the challenges can be overcome but might also lead to newer ones.

THE OPPORTUNITIES FOR HETEROGENEOUS INTEGRATION

Above are the major challenges that the next-gen XPU powered using heterogeneous integration may face. However, there are several opportunities also that the heterogeneous integration provides.

The two major opportunities for the semiconductor industry if heterogeneous integration is adopted at a large scale:

Emerging Solutions: The solutions that heterogeneous integration can enable will be novel that can take the best of the IPs and integrate them to form an efficient computing system. These systems might very well provide high-performance computing to the general-purpose domain. The area to power wall can be overcome using heterogeneous integration and will drive design to packaging solutions. The only key is large scale usage as is the case with monolithic chips.

Cost Optimization: Yield is one of the major concerns when a single die is fabricated to manufacture XPU. With heterogeneous integration, there is a possibility to design and manufacture dies separately. It can bring down the wastage and improve yield, which in-turn will lower the cost and will certainly improve manufacturing efficiency.

The time of heterogeneous integration has come. Emerging solutions have started to embrace the possibilities heterogeneous integration provides. It will be interesting to see how general-purpose computing changes with heterogeneous integration design and manufacturing.