- EDITORIAL | INDUSTRY OBSERVER

# Wafer-Level Yield Signatures: Types, Detection, Challenges & Cost Implications

Chetan Arvind Patil Contributing Writer | EPDT

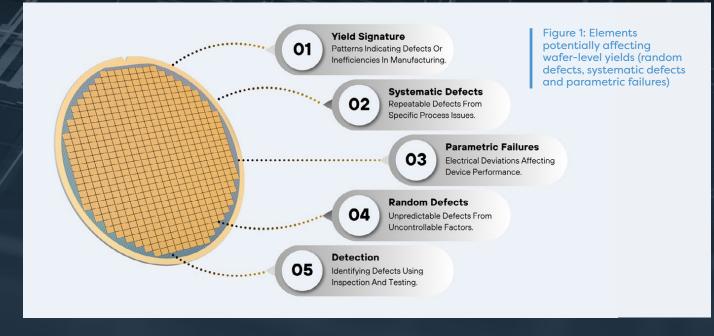

Wafer-level yield is a key metric in semiconductor manufacturing - representing the proportion of functional chips produced on a wafer after fabrication. It is a critical indicator of production efficiency, directly impacting on costs, quality and competitiveness. Beyond this numerical measure, yield signatures, distinct patterns and anomalies observed on wafers provide valuable insights into the manufacturing process. These signatures help identify the causes of defects and reveal process inefficiencies, guiding corrective actions to enhance overall yield. Understanding the different types of yield signatures is essential for targeted detection and analysis.

One common type of yield signature is random defects, which arise from uncontrollable factors - such as particle contamination, random process variations, or external environmental influences. These defects are typically unpredictable and unevenly distributed across the wafer, making them particularly challenging to address. While stringent cleanroom protocols and advanced process control can reduce their occurrence, random defects cannot be totally eliminated, requiring manufacturers to focus on continuous monitoring and mitigation strategies.

In contrast, systematic defects result from repeatable issues within the manufacturing process, such as equipment malfunctions, misaligned lithography, or inconsistencies in the materials used. Unlike random defects, systematic defects form distinct patterns such as rings, clusters, or radial alignments - making them easier to identify and diagnose. By analysing these patterns, manufacturers can pinpoint specific process steps or items of equipment that require adjustment, thereby improving yield efficiency.

A 3rd category, parametric failures, occurs when a device's electrical performance deviates from its intended specifications. Parameters like threshold voltage, leakage current, or drive strength may drift outside acceptable limits, impacting on device reliability and performance. While parametric failures may not result in outright defects, they degrade the overall quality of the wafer, thus emphasising the need for detailed parametric analysis to ensure consistent device functionality.

Each type of defect, random, systematic, or parametric, presents unique challenges and requires tailored detection and analysis methods. Together, they form a comprehensive picture of wafer-level yield, enabling manufacturers to refine their processes, enhance production efficiency and deliver high-quality semiconductor devices.

#### **Detection of wafer-level yield signatures**

The detection of wafer-level yield signatures is a crucial aspect of semiconductor manufacturing. It allows engineers to identify and resolve defects that impinge on device functionality and production efficiency. Yield signatures, which appear as specific patterns or trends across wafers, provide critical insights into issues ranging from random defects caused by contamination though to systematic process failures or parametric deviations. Effective detection requires a combination of advanced inspection methods, automated tools and sophisticated analytics, to ensure precision and reliability.

A foundational method for detecting yield signatures is optical inspection, which uses high-resolution imaging systems to scan wafers for visible anomalies - such as scratches, particles, or irregular patterns. Automated optical inspection (AOI) tools enhance this process by integrating imaging capabilities with powerful algorithms that rapidly identify and classify defects. AOI proves particularly effective in the detection of systematic defects (like ring or scratch patterns or radial misalignments), which may go unnoticed during manual inspections. These tools improve detection accuracy and accelerate the process, ensuring high throughput in modern fabs.

Another critical technique is electrical testing, which evaluates the performance of individual chips on a wafer. Parametric testing, for instance, measures key electrical characteristics

####

(such as leakage current, threshold voltage and resistance) against predefined specifications. Any deviations from these specifications can signal parametric failures, often linked to subtle process inconsistencies that do not manifest as physical defects. Advanced wafer probing systems further enhance this process by providing detailed, real-time data on each chip's electrical performance, enabling precise identification of problem areas.

Defect mapping is an equally vital tool in yield signature detection. Engineers can create visual maps highlighting defect locations and patterns across the wafer by aggregating data from optical inspections and electrical tests. These maps help identify issues - such as clustered defects caused by localised equipment failures or concentric rings that are indicative of chemical or mechanical inconsistencies. By visualising these patterns, engineers can target specific process steps or equipment for improvement, streamlining their troubleshooting efforts. Modern yield detection also leverages data analytics to boost accuracy and predictive capabilities. Statistical process control (SPC) enables real-time monitoring of critical process parameters - thereby helping to detect anomalies before they escalate into significant yield losses. Such tools can identify correlations between defects and specific manufacturing conditions across large datasets when combined with machine learning (ML) algorithms and suchlike. This predictive approach enhances defect detection, allowing manufacturers to anticipate and address yield issues proactively.

Emerging technologies are also revolutionising yield signature detection. Artificial intelligence (AI) technology is being increasingly integrated into inspection tools, enabling the recognition of intricate defect patterns and adaptive learning from historical data. Advanced imaging techniques, such as infra-red (IR) and X-ray inspection, are also gaining prominence because of their ability to

| Challenge                                      | Description                                                                                                     | Impact                                                                                                  |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Miniaturisation of technology nodes.           | Smaller nodes (e.g. 3nm) require advanced tools to detect microscopic defects.                                  | Difficult to identify subtle process variations<br>and parametric failures.                             |

| Increasing design complexity.                  | Modern chips, with billions of transistors and 3D stacking, introduce additional defect possibilities.          | Longer detection times and increased complexity in defect analysis.                                     |

| Variability in manufacturing processes.        | Process variations, like temperature or material differences, cause unpredictable random defects.               | Can be hard to link defects to specific process steps, complicating corrective actions.                 |

| Limitations of inspection tools.               | Conventional tools struggle with sub-surface or latent defects (e.g. micro-cracks, voids, etc.).                | Invisible defects may remain undetected, affecting device reliability.                                  |

| Data overload and analysis bottlenecks.        | Massive amounts of data from various sources require real-time, scalable analysis.                              | Slower defect detection and delayed yield optimisation.                                                 |

| Distinguishing random from systematic defects. | Random defects may mimic systematic patterns, complicating differentiation.                                     | Ineffective corrective measures, due to misclassification.                                              |

| Evolving defect patterns.                      | New materials and processes introduce previously unseen defect modes.                                           | Detection tools and algorithms must continuously adapt, increasing the associated costs and complexity. |

| Cost constraints.                              | High-precision tools for yield detection<br>are expensive and may be inaccessible<br>for smaller manufacturers. | Balancing detailed analysis with production<br>budgets can prove difficult.                             |

Table 1: Wafer-level yield signature detection challenges

# NEWS & ANALYSIS

identify sub-surface defects that conventional optical systems cannot uncover. These innovations are particularly beneficial in tackling the growing complexity of semiconductor devices, ensuring more comprehensive and accurate yield detection.

# Challenges in detecting waferlevel yield signatures

The detection of yield signatures is a critical aspect of semiconductor manufacturing, proving pivotal in resolving the defects impacting on production efficiency and device reliability. However, the increasing complexity of modern semiconductor processes and devices based upon them has introduced significant challenges in detecting and analysing these signatures. From microscopic defects at advanced technology nodes to the vast datasets generated during manufacturing, yield detection has become more intricate and demanding. Understanding these challenges is essential for developing innovative solutions and maintaining competitiveness in the semiconductor industry. Table 1 summarises the significant challenges in detecting wafer-level yield signatures.

# Cost implications of wafer-level yield

From a cost perspective, wafer-level yield is a critical factor in semiconductor manufacturing, directly impacting production efficiency and profitability. A higher yield translates into more functional chips per wafer, reducing the cost per unit, while lower yields increase the cost of each functional chip due to defects. Even a tiny drop in yield can have significant financial ramifications - especially in advanced nodes where the price of a single wafer can exceed tens of thousands of pounds/dollars. For instance, a 1% yield loss at such nodes can lead to millions in lost revenue.

Random, systematic and parametric failures all contribute to yield losses, each adding to costs in unique ways. Random defects often demand investments in advanced cleanroom protocols and process control technologies to mitigate their impact. Systematic defects may require expensive process redesigns, equipment upgrades, or the retraining of personnel to address recurring issues. Parametric failures, which degrade chip performance without causing outright defects, can reduce market value, as well as increasing testing and sorting costs. Low wafer-level yield also incurs indirect costs - such as additional resources for failure analysis, rework and retesting. Delays addressing recurring yield issues can postpone product launches, thus having a negative effect on a company's roadmap and market position. In many cases, companies must overproduce wafers to meet demand, further inflating production costs.

These financial pressures are especially pronounced in ultra-advanced nodes (7nm or smaller), where manufacturing complexity and defect sensitivity are higher. Yield challenges in such technologies can constitute a substantial proportion of production expenses, making yield improvement a top priority. Manufacturers also have to invest in advanced defect detection tools, Al-powered analytics and robust process control systems to manage these cost implications. In all, by addressing yield losses early and optimising production processes, semiconductor companies can minimise waste, reduce costs and maintain their competitiveness.

### IoT SoC Specialist Raises \$8million in Financial Backing

Chennai-located IoT system-on-chip (SoC) development company Mindgrove has successfully drawn in \$8 million during its series A funding round. This follows on from \$2.3 in seed funding being secured in early 2024. The start-up has been identified as one of India's foremost prospects, with the monetary resources

now made available helping it recruit further staff and expand its engineering resources, as well as enabling promotion of its capabilities internationally. Among those contributing funds are Rocketship, Speciale Invest, Mela Ventures, Peak XV and Whiteboard Capital.

# Mouser Recognised by Bourns for Supply Chain Accomplishments

Mouser Electronics has been made the recipient of leading passive components supplier Bourns' e-Commerce Distributor of the Year award. This is the latest in a long line of accolades that Mouser has gained from Bourns over the last decade, and underlines the continued success of the partnership between these companies. Currently 46,000 Bourns parts are available to order via Mouser - including inductors, resistors, circuit protection devices, potentiometers, shunt-based current sensors, etc.

## TDK MEMS Devices Pivotal to Al-Powered Smart Cane

An array of MEMS-based sensors from TDK have been incorporated into London-situated start-up WeWALK's Smart Cane 2. Helping the visually impaired to enjoy independent living, this intelligent assistive product enables high precision navigation and obstacle avoidance. A 6-axis InvenSense

SmartMotion IMU is complemented by SmartSonic ultrasound timeof-flight (ToF) sensor hardware - providing the user with environmental/ contextual awareness. The built-in AI-powered voice assistant function is then served by InvenSense MEMS microphones. These accurately capture voice commands, while only drawing minimal power budget.

## Quantum Resistant Chip Start-Up Gains Millions in Funding

Geneva-based specialist in post-quantum cryptography (PQC) SEALSQ has now generated \$60 million in funding to further its commercial progression. New funds were raised via support from Maxim Group following its latest share offering. Founded in 2022, the company is traded on the NASDAQ. Last summer it announced the introduction of 2 quantum resistant chips - the QS7001 and QVault TPM. Using RISC-V technology, these are aimed at enabling the security needed by critical IoT infrastructure.